# **AW-CU570**

# Wi-Fi 6 1x1 + Bluetooth Low Energy 5.3 / 802.15.4

## **Microcontroller Module**

# Layout Guide

Rev. 01

(For Standard)

### **Revision History**

| Version | Revision<br>Date |   | Description     | Initials  | Approved  |

|---------|------------------|---|-----------------|-----------|-----------|

| 01      | 2023/12/04       | • | Initial Version | Roger Liu | N.C. Chen |

|         |                  |   |                 |           |           |

|         |                  |   |                 |           |           |

|         |                  |   |                 |           |           |

#### INTRODUCTION

This document provides key guidelines and recommendations to be followed when creating AW-CU570 layout. It is strongly recommended that layouts be reviewed by the AzureWave engineering team before being released for fabrication. The following is a summary of the major items that are covered in detail in this application note. Each of these areas of the layout should be carefully reviewed against the provided recommendations before the PCB goes to fabrication.

- 1. GENERAL LAYOUT GUIDELINES

- 2. "PRINTED ANTENNA" LAYOUT PATTERN SUGGESTION

- 3. LOAD-BOARD PADS OPENING SUGGESTION

- 4. LOAD-BOARD STENCIL THICKNESS / STENCIL OPENING SUGGESTION

- 5. MECHANICAL CHARACTERISTICS

#### **1. GENERAL LAYOUT GUIDELINES**

#### **Power Layout**

- B\_3V3 and M\_3V3 are both main power pads of internal IC. Keep their impedance as low as possible and place a 10uF decoupling capacitor close to both pins that is used to decouple high frequency noise at digital and RF power terminals.

- In order to reduce PCB's parasitic effects, placing more via on ground plane is better.

- Make sure every power traces have good return path (ground path).

#### **Ground Layout**

- Each ground pad of components on top layer should have via drilled to PCB layer 2 and via should be as close to pad as possible. A bulk decoupling capacitor needs two or more.

- Don't place ground plane and route signal trace below printed antenna or chip antenna to avoid destroying its electromagnetic field, and there is no organic coating on printed antenna.

- Move GND vias close to the pads.

#### **Digital Signal Integrity And Routing**

- If Layer 1 and Layer 2 are selected for digital signal routing, it is important that no signal traces are routed underneath external components such as bypass capacitors, power rail filtering beads, etc. Otherwise, noise coupling may occur.

- Keep SPI traces away from all clock lines and noisy power supply components such as the switcher inductors. Avoid crossing over power supplies or ground discontinuities. Ideally, the SPI traces should have a solid ground

on the layer adjacent to them. Of key importance is the SPI clock routing.

#### **Digital Interface**

- The digital interface to the module must be routed using good engineering practices to minimize coupling to power planes and other digital signals.

- The digital interface must be isolated from RF trace.

#### **Sleep Clock Signal**

External 32.768KHz is an option for AW-CU570 (Pin A3/GPIO\_22)

- Don't mix power line close to OSC signal line.

- Please make sure there are no signal lines which are variant rapidly, crossing with the oscillator signals.

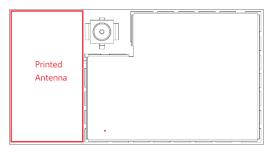

#### **Printed Antenna Layout Pattern Suggestion**

- Please put the antenna side at the edge of your system board for better antenna performance.

- Please keep the printed antenna area clear without any copper below it.

- In order to achieve best antenna performance, we suggest you expand the copper prohibition area of your system board when the area near printed antenna or put printed antenna area of module out the edge of your system board.

| Expand the copper prohibition area | Adaptor Board |

|------------------------------------|---------------|

| Printed<br>Antenna                 |               |

|                                    |               |

4

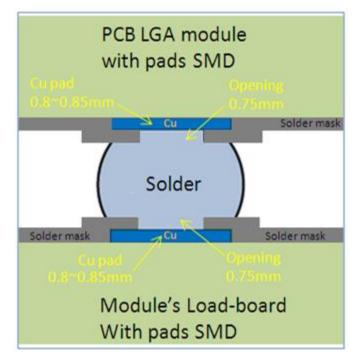

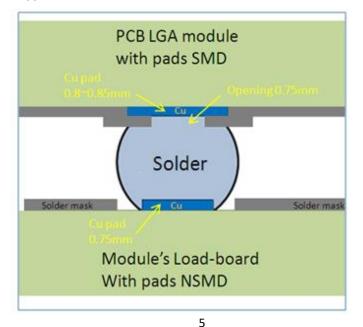

#### 2. Load-board Pads Opening Suggestion

AW-CU570 LGA pads design with SMD (Solder Mask Defined).

- For customer using pads SMD (Solder Mask Defined)

- Cu Pad size suggestion: 0.85mm

- Pads opening suggestion: 0.75mm

- For customer using pads NSMD (Non-Solder Mask Defined)

- Cu Pad size suggestion: 0.75mm

Note: Choice of SMD or NSMD is determined by the customer, Azurewave recommend using SMD (Solder Mask Defined). This suggestion just for customer reference, please discuss with AzureWave engineer before you start SMT.

#### 3. load-Board Stencil Thickness / Stencil Opening Suggestion

- Stencil thickness : 0.10~0.12mm

- Stencil opening with pads suggestion: 0.75mm

Note: This suggestion just for customer reference, please discuss with AzureWave engineer before you start SMT.

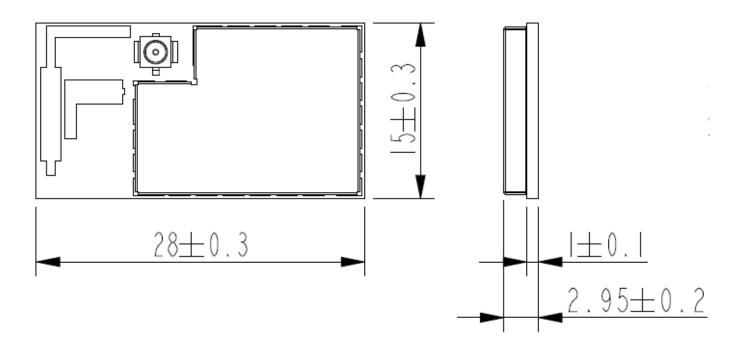

#### 4. Mechanical Characteristics

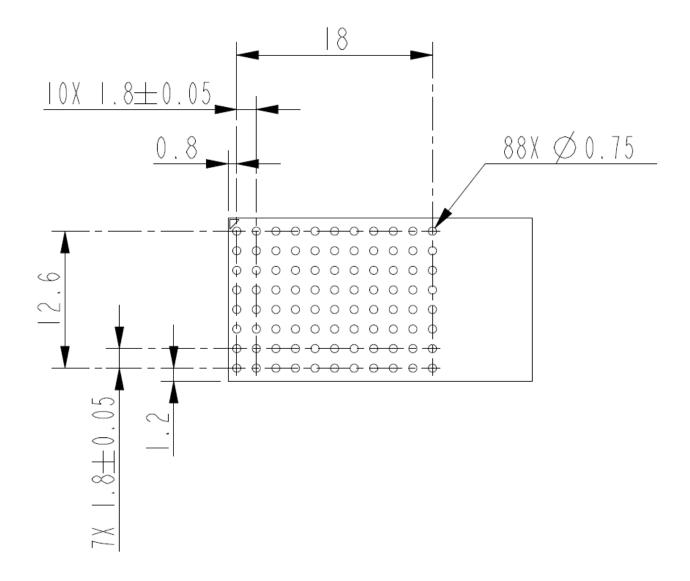

The size and thickness of the AW-CU570 LGA package module is listed below:

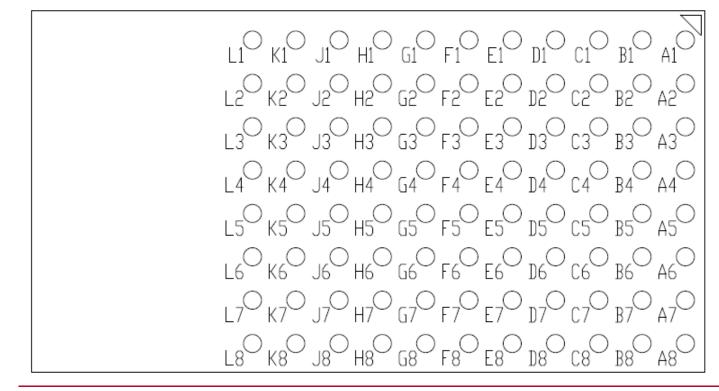

### (a)4.1 AW-CU570 PCB Layout Footprint

**TOP VIEW**

### (b)4.2 AW-CU570 Drawing